AMD Xilinx Website

AMD University Program

Adaptive Computing Support – Design Hubs

Kris K26 SoM

Kris Adaptive SoMs

Kris K26 SoM

Boot Firmware Overview

Kria GitHub.io Documentation Page

Kria Robotics Stack (KRS)

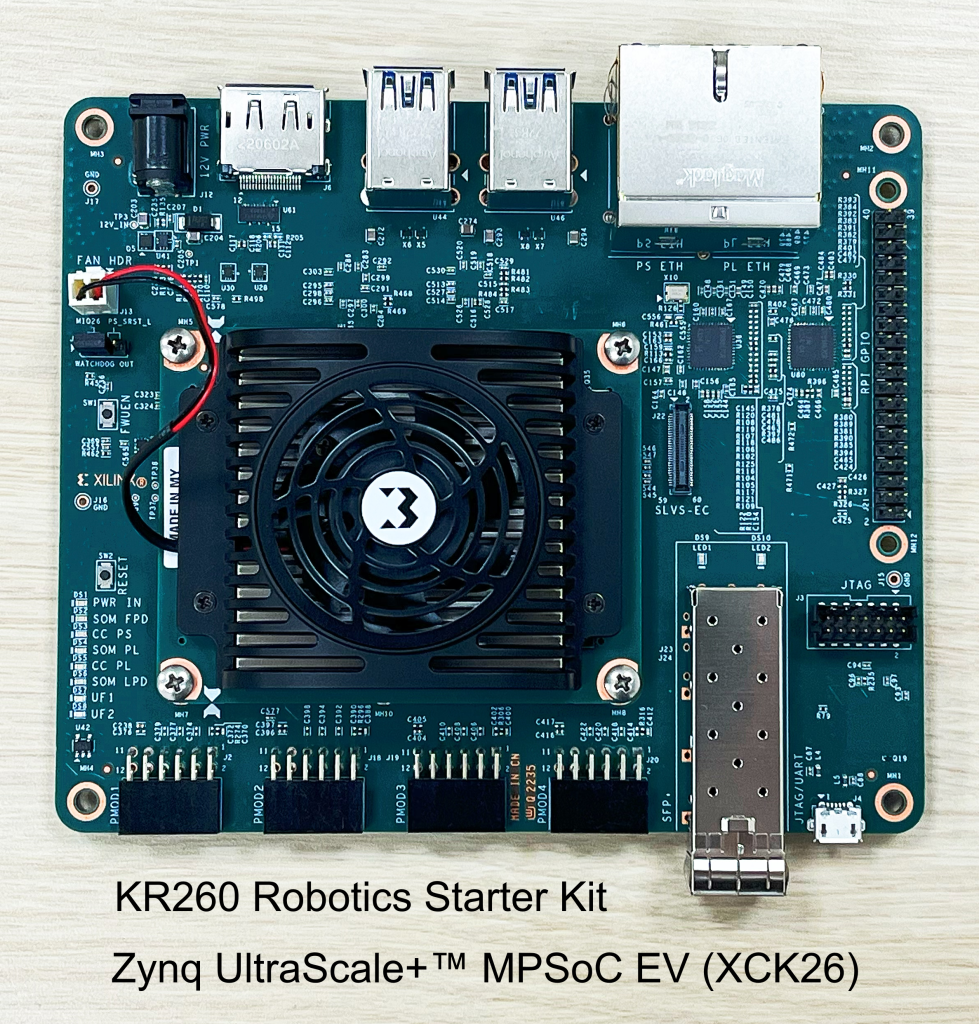

Getting Started with Kria KR260 Robotics Starter Kit

Using Accelerated Applications with the Kria K260 Robotics Starter Kit

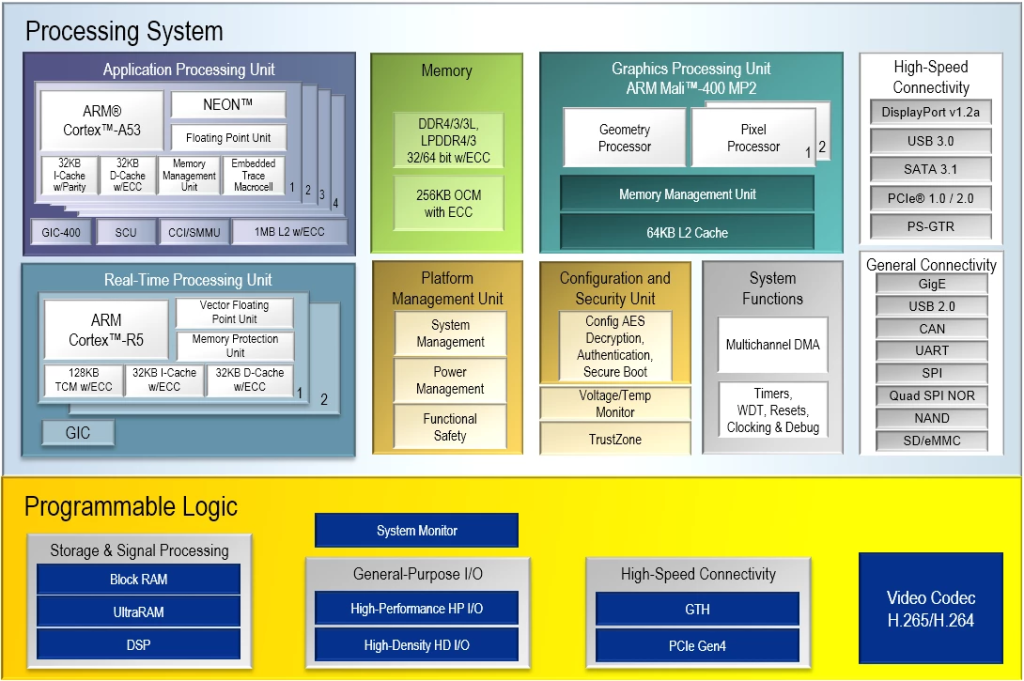

Zynq UltraScale+ MPSoC EV (XCK26)

APU: 64-bit Quad-Core Arm® Cortex®-A53 (up to 1.5GHz)

RPU: 32-bit Dual-Core Arm Cortex-R5F (up to 600MHz)

GPU: Arm Mali™-400MP2 (up to 667MHz)

VCU: H.264/H.265

Programmable Logic: 256K System Logic Cells

DSP Slices: 1248

Block RAM (BRAM) Blocks: 144

UltraRAM (URAM) Blocks: 64

Memory: 26.6Mb On-Chip SRAM

DDR4 Memory: 4GB 64-bit DDR4 (for PS)

Primary Boot Memory: 512Mb QSPI

Secondary Boot Memory: SDHC Card / eMMC

The development board I used to learn Xilinx FPGA

Back to top of the page